This is a read-only archive of an earlier blog posting. Reasons for the

change are at http://blog.sensicomm.com.

The permanent version of this post - with comments (if any) - is at

http://sensicomm.blogspot.com/2014/07/parallel-port-jtag.html

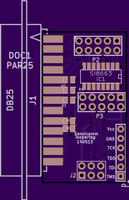

Parallel port jtag

I've been using a homebrew version of

the Xilinx DLC5 parallel port jtag adapter for programming my fpga

boards. The DLC5 is no longer supported by Xilinx, but some Linux

jtag programmers still support it.

Recently I moved to a

new PC, and my DLC5 hack no longer works with that parallel port. I

can see on the scope that the right pins are moving, but the chip

won't program. I suspect that either the rise and fall times are

too slow, or there's noise on the signal lines.

Anyway,

I had a sample of the SiLabs si8663 digital isolator, so I decided

it's time to build a new interface. The Si8663 is a hex isolator (3

signals each direction), that's spec'ed to operate up to 150 Mbps

bit rate (WAY more than needed for this app). Another neat feature

is that the drivers on each side work from 2.5 to 5.5 volts,

providing a level shifter at no extra charge.

Board is

available on OshPark (www.oshpark.com) for anyone interested.

Project name is "isopartag 140513". Circuit's simple: chip + 4

bypass caps on the bottom. The design includes resistors to tap

power from unused pins of the parallel port, but they haven't been

added yet, to that feature is untested. For now I just tap 5 volts

from an unused keyboard or mouse port.

Caution:The Si8663 comes

in two versions: a wide body for safety isolation, and a narrow

body intended more for electrical noise isolation. I'm using the

narrow version, and the board is not designed with wide separation

between the input and output sides. In other words, this design is

for low voltages only,

don't use it where safety is an

issue.Comments on blogspot.com

To make or view comments, see the original post at

http://sensicomm.blogspot.com/2014/07/parallel-port-jtag.html